[제52주차 IR52 장영실상] 삼성전자 / 광대역폭 메모리 플래시볼트

등록일 2020-12-30

▲왼쪽부터 삼성전자 백철호 연구원, 손교민 마스터, 천기철 연구원, 김구영 연구원.

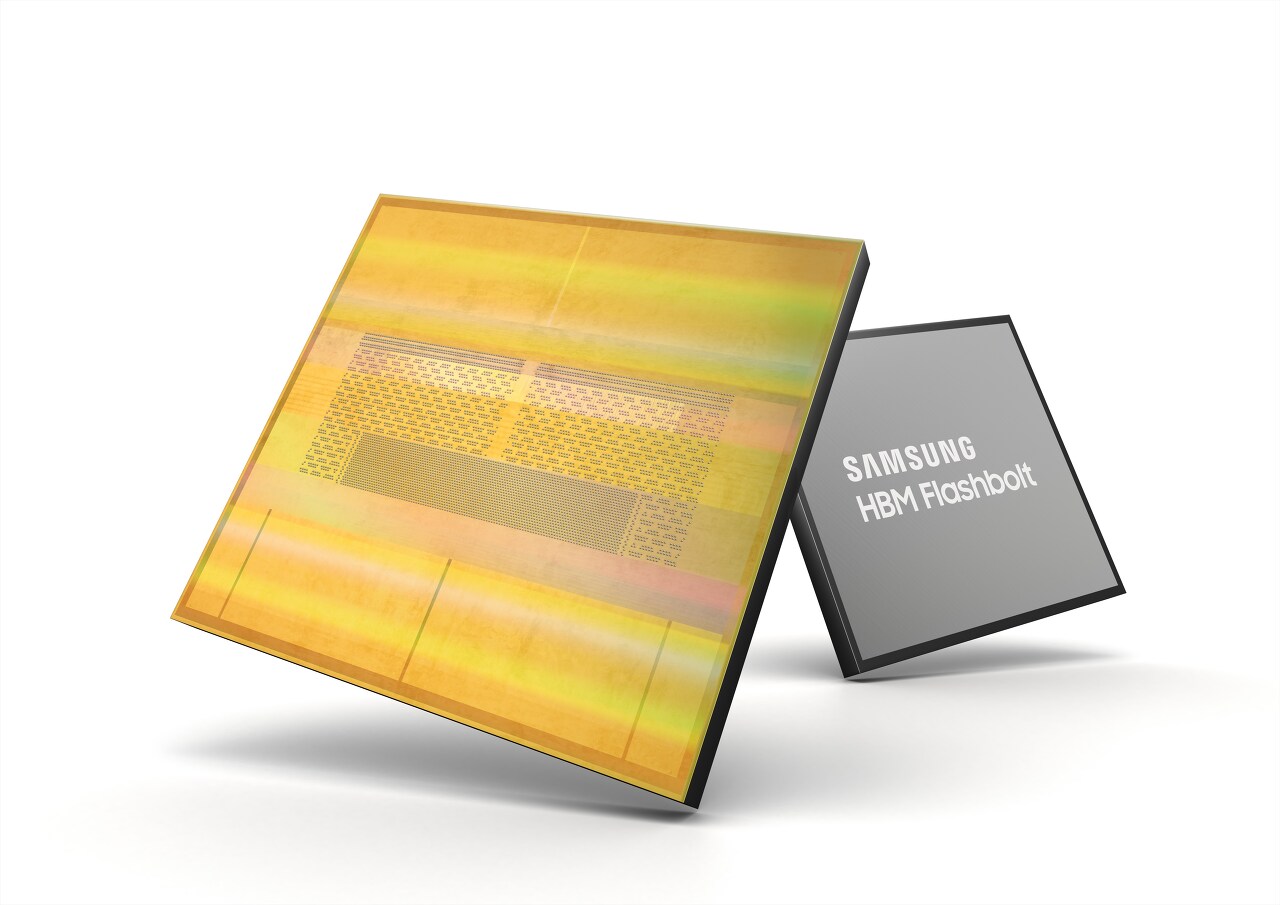

삼성전자가 개발한 `광대역폭 메모리 플래시볼트(HBM2E Flashbolt TM)`가 올해 주간 단위 장영실상 시상으로는 마지막인 52주차 iR52 장영실상을 수상했다. 메모리 플래시볼트는 슈퍼컴퓨터 연산을 위한 고성능·대용량 메모리 D램(반도체 기억소자)이다. 삼성전자는 "기존 제품보다 더 많은 용량과 더 높은 속도를 원하는 고객사들 요청을 충족시키기 위해 개발에 들어가 성공했다"며 "인공지능(AI) 가속기가 필요로 하는 성능을 만족시킬 수 있는 유일한 메모리 제품"이라고 강조했다. 이 제품은 국제반도체 표준화 기구에서 표준화를 진행하고 있는 고성능 그래픽 D램(GDDR6)과 비교했을 때도 월등한 성능을 자랑한다. 면적은 고성능 그래픽 D램의 절반 수준이지만 용량은 4배가량 크고, 초당 2.8배 많은 데이터를 처리할 수 있다. 전력도 기존 제품에 비해 3분의 1가량 덜 들어간다. 세계 최초로 개발한 12단 적층 기술이 적용된 덕분이다. 머리카락 20분의 1 이하 수준 굵기인 실리콘관통전극(TSV) 6만개를 연결하는 3D-TSV 첨단 패키징 기술을 적용했다. 공정을 마친 복수의 칩을 위로 얇게 쌓아올려 하나의 반도체로 구성해 전체 면적은 줄어들고 용량은 크게 늘어난 메모리 구현이 가능했다는 게 삼성전자 측 설명이다. 삼성전자는 "광대역폭 메모리 플래시볼트 D램 주요 거래처는 미국·중국·일본 슈퍼컴퓨터, 딥러닝 AI 응용, 고성능 그래픽 시스템, 5G 등 네트워크 서비스 업체"라며 "2024년까지 5년간 2조4000억원 규모 수출을 기대하고 있다"고 전했다.

삼성전자 연구팀은 "AI 발전뿐 아니라 5G를 위한 고속 네트워크 서버와 슈퍼컴퓨터에 이르기까지 광대역폭 메모리 플래시볼트 활용도가 무궁무진하고, 용량과 성능에 대한 요구 사항이 계속 높아지고 있다"며 "용량 관점에서는 16단 적층 제품까지 개발하고, 성능 관점에서도 현재 4.2Gbps보다 월등히 높은 6.4Gbps 이상의 제품을 개발할 것"이라고 말했다.

삼성전자

HBM2E FlashboltTM

회사명 : 삼성전자대표자 : 김기남제품명 : HBM2E FlashboltTM모델명 : KHAA84901B, KHAA44801B개발기술명 : 차세대 AI 및 슈퍼컴퓨터용 세계 최대전송량 3세대 초고속 HBM2E 기술 개발선정분야 : 전기.전자

제품소개 용도 및 기능HBM2E Flashbolt TM은 슈퍼컴퓨터의 연산을 위한 고성능, 고용량 D램입니다. 초고속 DRAM으로 흔히 사용되는 GDDR6와 비교 시, 3D TSV 적층 기술을 적용하여 55% 작은 면적, 4배 많은 용량, 초당 2.8배 많은 데이터 처리, 26% 우수한 전력 효율(BW/Power)이 가능합니다. 데이터센터에서의 AI/딥러닝, 클라우드 및 5G 등 고성능, 고용량, 초연결, 초고속 DRAM 솔루션을 제공 가능합니다. 차별적 특징첫 번째로는 3D 고속 회로 기술인 Data-bus window 확장 및 3D PHY-TSV 최단 배치 기술로 초고성능, 초절전 메모리 시스템 개발 솔루션을 제공하였습니다. System 평가 결과 세계 최고 데이터 전송 속도 4.2Gpbs를 달성을 확인할 수 있었습니다. 두 번째로는 Thin Wafer Handling 공정 기술을 통해 세계 최초 12단 적층 기술 개발에 성공하여 HBM 패키지 기술 한계를 돌파할 수 있었습니다. 이 기술에는 머리카락 굵기 1/20 이하 TSV(Through Silicon Via) 6만개를 초정밀 연결하는 3D-TSV(3차원 실리콘 관통전극) 첨단 패키징 기술이 적용되어 있습니다. 세 번째로는 HBM 사상 OD-ECC 최초 탑재하였으며, 시스템과 상호 보완된 HBM2E 특화 회로 기술을 적용하여 고온, 고용량 제품의 신뢰성을 확보할 수 있었습니다. 이를 통해 105도 품질 보증은 물론 Refresh 개선으로 시스템 성능 향상이 가능하였습니다. 마지막으로는 2.5D 조립 불량 테스트를 위한 MBIST(Memory Built-In Self-Test) & Repair 기술 혁신으로 테스트 시간을 65% 감소시킬 수 있었습니다. 즉, SiP 조립 후 System 테스트 시간 단축을 통한 양산성 확보가 가능하였습니다. 담당부서삼성전자 DS부문 기획팀(03180964656)

'판교핫뉴스1' 카테고리의 다른 글

| 회계개혁 시장안착 지원을 위한「외부감사법 시행령」개정안 국무회의 통과 (0) | 2021.01.05 |

|---|---|

| 기능성 소재를 밀가루 반죽처럼 입맛대로 ‘요리’ 한다-액체 갈륨에 그래핀을 넣으면 전자파 차폐 소재로, 다이아몬드를 섞으면 방열 소재로 변신 (0) | 2021.01.05 |

| [제51주차 IR52 장영실상] 현대자동차 `전륜 대형 습식 8속 더블 클러치 변속기` (0) | 2021.01.05 |

| [제50주차 IR52 장영실상] 아이벡스메디칼시스템즈 / 고압산소치료기 (0) | 2021.01.05 |

| 비전형상표(입체ㆍ소리ㆍ색채 등) 상표심사기준 개정-새로운 형태의 상표에 대한 심사 정확성 향상 및 출원인 편의 제고 기대 (0) | 2021.01.05 |