“더 작고, 더 빠르게”반도체 미세공정 한계 돌파 가능한 신소재 개발-울산과학기술원(UNIST)과 삼성전자 종합기술원, 반도체 미세공정 한계 돌파 가능한 신소재 개발

기초연구진흥과 작성일 2020.06.25.

“더 작고, 더 빠르게”

반도체 미세공정 한계 돌파 가능한 신소재 개발

- 반도체 내부 전기 간섭 최소화하는 소재 개발로 집적도·성능 향상 가능 -

- 울산과학기술원-삼성전자 종합기술원 공동연구, 네이처 논문 게재 -

□ 반도체 칩 안의 소자를 “더 작게” 만들 수 있는 새로운 소재가 개발되었다. 이 소재를 이용하면 메모리와 같은 반도체 칩의 작동 속도를 “더 빠르게” 만들 수 있을 것으로 기대된다.

□ 울산과학기술원(UNIST) 자연과학부 신현석 교수팀이 삼성전자 종합기술원의 신현진 전문연구원팀, 기초과학연구원(IBS) 등과 국제공동연구를 통해 반도체 소자를 더 미세하게 만들 수 있는 ‘초저유전율* 절연체**’를 개발하는데 성공했다.

* 유전율 : 외부 전기장에 반응하는 민감도를 의미하며, 유전율이 낮으면 전기적 간섭이 줄어들어 반도체 소자 내 금속 배선(전류가 흐르는 길)의 간격을 줄일 수 있음

** 절연체 : 전류가 흐르지 않는 물질을 의미하며, 반도체 소자 내 금속 배선에서 전자가 다른 부분으로 이탈하는 것을 막기 위해 전자이동경로 사이에 절연체를 삽입함

◦ 반도체 소자의 크기를 줄임과 동시에 정보처리속도를 높일 수 있는 핵심적인 방법이 절연체의 유전율을 낮추는 것인데, 공동 연구팀이 기존 절연체 보다 30% 이상 낮은 유전율을 갖는 ‘비정질 질화붕소* (amorphous boron nitride) 소재’를 합성하는데 성공한 것이다.

* 원자 배치가 규칙적인 육방정계 질화붕소(일명 화이트그래핀)와 달리, 원자 배치가 불규칙한 질화붕소

◦ 과학기술정보통신부(장관 최기영)와 UNIST(총장 이용훈)는 이번 성과가 세계 최고 권위의 학술지 네이처(Nature, IF 43.070)에 6월 25일 0시(한국시간) 게재되었다고 밝혔다.

□ 현재와 같은 나노미터 단위의 반도체 공정에서는 소자가 작아질수록 내부 전기 간섭 현상이 심해져 오히려 정보처리 속도가 느려지게 된다. 이러한 이유로 전기 간섭을 최소화하는 낮은 유전율을 가진 신소재 개발이 반도체 한계 극복의 핵심이라고 알려져 있다.

<‘15년 국제반도체기술로드맵(ITRS: International Technology Roadmap for Semiconductors)>

‣트랜지스터의 세대가 거듭될수록 유전율이 낮은 절연체의 개발이 필수적이며, 초저유전율 소재 개발이 반도체 집적회로의 집적화의 한계점 중 하나임

◦ 현재 반도체 공정에서 사용되는 절연체는 다공성 유기규산염(p-SiCOH)으로 유전율이 2.5 수준이다. 이번에 공동연구팀이 합성한 비정질 질화붕소의 유전율은 1.78로 기술적 난제로 여겨진 유전율 2.5이하의 신소재를 발견한 것이며, 이를 통해 반도체 칩의 전력 소모를 줄이고 작동 속도도 높일 수 있을 것으로 기대된다.

◦ 연구팀은 이론적 계산 및 포항가속기연구소 4D 빔라인을 활용해 비정질 질화붕소의 유전율이 낮은 이유가 ‘원자 배열의 불규칙성’ 때문이라는 점도 밝혀냈다.

◦ 뿐만 아니라, 기존에는 유전율을 낮추기 위해 소재 안에 미세한 공기 구멍을 넣어 강도가 약해지는 문제가 있었으나, 비정질 질화붕소는 물질 자체의 유전율이 낮아 이러한 작업 없이도 높은 기계적 강도를 유지할 수 있게 되었다.

□ 제1저자인 홍석모 UNIST 박사과정 연구원은 “낮은 온도에서 육방정계 질화붕소(화이트 그래핀)가 기판에 증착되는지 연구하던 중 우연히 ‘비정질 질화붕소’의 유전율 특성을 발견했고, 반도체 절연체로써 적용 가능성을 확인했다”고 연구과정을 밝혔다.

ㅇ 교신저자인 신현석 UNIST 교수는 “이 물질이 상용화된다면 중국의 반도체 굴기와 일본의 수출 규제 등 반도체 산업에 닥친 위기를 이겨내는 데 큰 도움이 될 것”이라며 “‘반도체 초격차 전략’을 이어갈 수 있는 핵심 소재기술”이라고 강조했다.

◦ 또한 공동 교신저자인 신현진 삼성전자 종합기술원 전문연구원은 “이번 연구결과는 반도체 산업계에서 기술적 난제로 여겨지던 부분에 대해 학계와 산업계가 상호 협력을 통해 해결방안을 찾아낸 모범적인 사례”라고 말했다.

◦ 뿐만 아니라, 유럽연합의 그래핀 연구 프로젝트(Graphene Flagship)*파트너인 영국 케임브리지 대학교 매니쉬 초왈라 교수와 스페인 카탈루냐 나노과학기술연구소 스테판 로슈 교수가 참여하여 국제 공동연구로 진행되었으며,

* 그래핀을 포함한 2차원 물질에 대한 연구 프로젝트로 약 1조 3,592억원(10억유로)을 투자하는 유럽 연합의 최대 규모 연구 프로젝트

◦ 연구 수행은 과학기술정보통신부의 기초연구실, 중견연구(전략) 및 기초과학연구원(IBS), 삼성전자의 지원으로 이루어졌다.

이 자료에 대하여 더욱 자세한 내용을 원하시면

과학기술정보통신부 김미미 사무관(☎ 044-202-4531)에게 연락주시기 바랍니다.

연 구 결 과 개 요

□ 연구배경

반도체 소자1)의 고집적화가 가속화됨에 따라, 소자의 크기는 점점 작아졌다. 전통적으로 칩(Chip)의 성능(속도)은 트랜지스터2)의 스위칭 속도3)에 좌우됐으나, 소자의 크기가 작아지면서 빠른 스위칭 속도보다 배선 구조에서 발생하는 ‘신호전달 지연4)(RC delay: R은 금속 배선의 저항, C는 금속 배선 사이의 유전체 커패시턴스)’이 칩의 작동 성능을 좌우하게 됐다.

따라서 RC delay를 감소하기 위해 집적회로 백엔드 공정(BEOL ,back-end-of-line)5)의 금속 배선 사이에 증착되는 유전체(절연체)6)의 유전율7)을 줄이거나 금속배선의 전기저항 감소가 절대적으로 필요하다.

2015 ITRS 로드맵(미국 반도체 산업협회 발간하는 보고서)에 따르면, 트랜지스터의 세대가 거듭될수록 요구되는 유전물질(절연체)의 유전율은 감소하고 2028년에는 유전상수 2.0 이하의 유전체 개발이 필요하다. 하지만 현존 기술로는 불가능해, 초저유전 소재 개발이 IC칩(집적회로)의 집적화에서 한계점 중의 하나로 지목됐다.

□ 연구내용

연구팀은 플라즈마를 도입한 화학기상증착 방법을 이용해 실리콘(Si), 실리콘산화물(SiO₂), 구리(Cu) 등의 BEOL에 사용되는 기판에 3㎚ 두께의 매우 얇은 비정질 질화붕소(a-BN, amorphous BN) 8) 박막 증착에 성공했다.

a-BN을 고분해능 투과전자현미경(TEM)으로 관찰했을 때 기존에 보고된 a-BN보다 결정성이 낮았다. 광학적으로는 많이 연구된 육방정계 질화붕소(화이트 그래핀)와는 확연히 차이가 나는 광학적 물성을 보였다.

또한 a-BN을 이용해 간단한 전기소자(캐패시터)9)를 만들어 유전율을 측정해 보았는데, 기존에 보고된 여러 초저유전물질들과 비교했을 때 상당히 낮은 유전율(1.78, 100 KHz의 교류전류 주파수), 1.16 (1 MHz의 교류전류 주파수)을 나타냈다.

유전율뿐만 아니라 기존에 보고된 물질과 비교했을 때 기계적 물성도 우수하다. 일반적인 절연체로 사용되는 실리콘산화물과 유사한 고밀도로, 높은 강도 갖고 있으면 실리콘이나 구리 기판과의 접착력이 매우 높다.

금속 원자의 이동을 막는 금속 확산 방지막10)으로도 적용이 가능하다. 실리콘 기판 위에 형성된 a-BN 박막 위에 코발트(Co) 금속을 증착한 후 온도를 600℃로 올려 코발트 금속 원자가 a-BN을 뚫고 실리콘 기판으로 이동하는지를 보는 ‘베리어 평가’를 실시했는데, 코발트 금속의 이동을 완벽히 막아내는 매우 우수한 방지막의 특성을 보였다.

분자동역학(molecular dynamic simulation)을 이용한 이론적인 계산(NEXAFS)과 분석 등으로 근본적으로 물질의 극성이 무작위 방향으로 배열돼 있어 굉장히 낮은 유전율을 보이는 것으로 규명됐다.

□ 기대효과

배선금속과 초저유전물질이 들어가는 후공정(BEOL)은 메모리뿐만 아니라 비메모리까지 반도체 산업 전 영역에 걸쳐 사용되는 기술이다. 새로운 초유전물질의 개발은 감소하고 있는 초고밀도 집적회로(Very-large-scale integration; VLSI) 집적도의 상승세를 또 한 번 끌어올리고 소자의 소형화를 가속화 할 수 있는 원천기술이 될 것으로 기대한다.

용 어 설 명

1. 반도체 소자

반도체 소자는 실리콘과 같은 반도체(전기 흐름을 조절하는 물질), 금속(도체, 전기가 잘 통하는 물질), 절연체(부도체, 전기가 안 통하는 물질)등으로 구성돼 있다. 각종 전자제품에 들어가는 반도체 칩의 경우 단위 소자(회로) 여러 개가 집적돼 있다. 소자 집적도 높아지면 반도체의 정보 처리 속도 등이 빨라진다.

2. 트랜지스터(transistor)

전자 신호 및 전력을 증폭하거나 스위칭(회로를 연결했다 끊었다)하는 데 사용되는 반도체소자 중 하나.

3. 스위칭 속도

전자소자 안에 스위치 역할을 하는 트랜지스터의 구동 속도를 나타내는 단어로, 일반적으로 0과 1을 구현하는 논리소자의 연산속도를 대변하는 단어로 사용되고, BEOL의 유전체의 유전율과 배선 금속의 간격에 많은 영향을 받는다.

4. 신호전달지연(signal delay or RC delay)

금속 사이에 유전체(절연체)가 있는 상태에서 금속에 전류가 흐르게 되면 마주 보고 있는 두 금속 면에 전자 또는 전하가 축적되는 대전 현상이 발생한다. 대전된 두 금속 가까이 또 다른 전류가 흐르면 대전된 전하 때문에 발생하는 전기장의 간섭을 받고 전류가 흐르는 속도가 달라지는 현상이 생긴다. 초고밀도 집적회로에서 전극 금속 간의 거리가 가까워지게 되면 이러한 현상이 더욱 뚜렷하게 발생한다.

5. 유전체 (dielectric substance)

반도체에 들어가는 절연체를 이르는 다른 말. 물질은 전기전도도(전자가 얼마나 잘 이동하느냐)에 따라 도체, 반도체, 부도체(절연체)로 구분 된다.

6. 유전율 (permittivity)

전기가 통하지는 않는 부도체라도 외부의 전기장에 반응하는데, 그 반응의 민감도를 나타낸다. 자석의 N-S극처럼, 물질을 구성하는 분자는 전기쌍극자(electric dipole)가 있는데, 외부 전기장을 받으면 무질서하게 놓여있던 전기쌍극자가 정렬해 내부에 전기장이 발생한다. 이 전기장을 이용해 전하(전자)를 축적 할 수 있다. 단위부피당 유전율은 물질 고유의 특성이며, 유전상수로 나타낸다. 금속은 무한대의 유전상수를 갖으며, 공기의 유전상수가 가장 낮다. 때문에 기존 초 저유전체 연구에서는 절연체에 미세한 기공을 만들어 유전상수를 낮추는 방법이 주를 이뤘다. 이번 실험에서 합성된 비정질 질화붕소의 경우 전기쌍극자의 분포가 무질서해 유전상수가 낮다. 참고로 반도체의 소자 중 축전기에는 유전상수(High-k)가 높은 물질이 필요하다.

7. BEOL (back-end-of-line)

전체 반도체 공정 중에 후공정에서 만들어지는 구조로 전기 소자 위에 구리와 같은 전극 금속을 배열하여 원하는 전기소자를 올바르게 작동시키도록 전선을 이어주는 공정 또는 구조를 부르는 단어이다. 전극 금속끼리 맞닿게 되면 전기소자가 독립적으로 작동하지 않게 되는데 이를 방지하기 위해서 금속과 금속 사이에 초 저 유전물질을 삽입하여 전극 금속이 서로 닿지 않게 분리한다.

8. 비정질 질화붕소 (amorphous boron nitride)

원자 배열이 규칙적이지 않은 물질을 비정질이라 한다. (원자 배열이 규칙적인 물질은 결정이라 함). 규칙적인 원자 배열을 갖는 육방정계(6각형 벌집모양) 질화붕소의 경우 그래핀(벌집모양으로 탄소원자 배치된 2차원 물질)과 원자 배치 모양이 닮았지만 육안으로 하얗게 보여 ‘화이트 그래핀’으로 불린다.

9. 축전기 (Capacitor)

금속과 금속 사이에 유전체가 있는 구조로, 두 금속에 전압을 가하면 유전체의 유전율에 맞게 전하가 축적되는데 이런 현상을 이용하면 물질의 유전 상수를 구할 수 있다.

10. 금속 확산 방지막(metal barrier)

반도체 소자는 금속, 절연체, 반도체로 이루어져 있는데 금속의 경우 강한 전기장이나 열에너지를 받으면 원자들이 진동하게 되고, 이 진동을 원동력으로 금속 원자가 원래 위치에서 벗어나 절연체나 반도체 영역을 침범하고 화학적 결합을 이뤄 물질의 성질을 변화시킨다. 따라서 금속 확산을 막아줄 수 있는 물질을 금속과 다른 물질 사이에 삽입하는데, 이 물질을 금속 확산 방지막이라 한다.

그 림 설 명

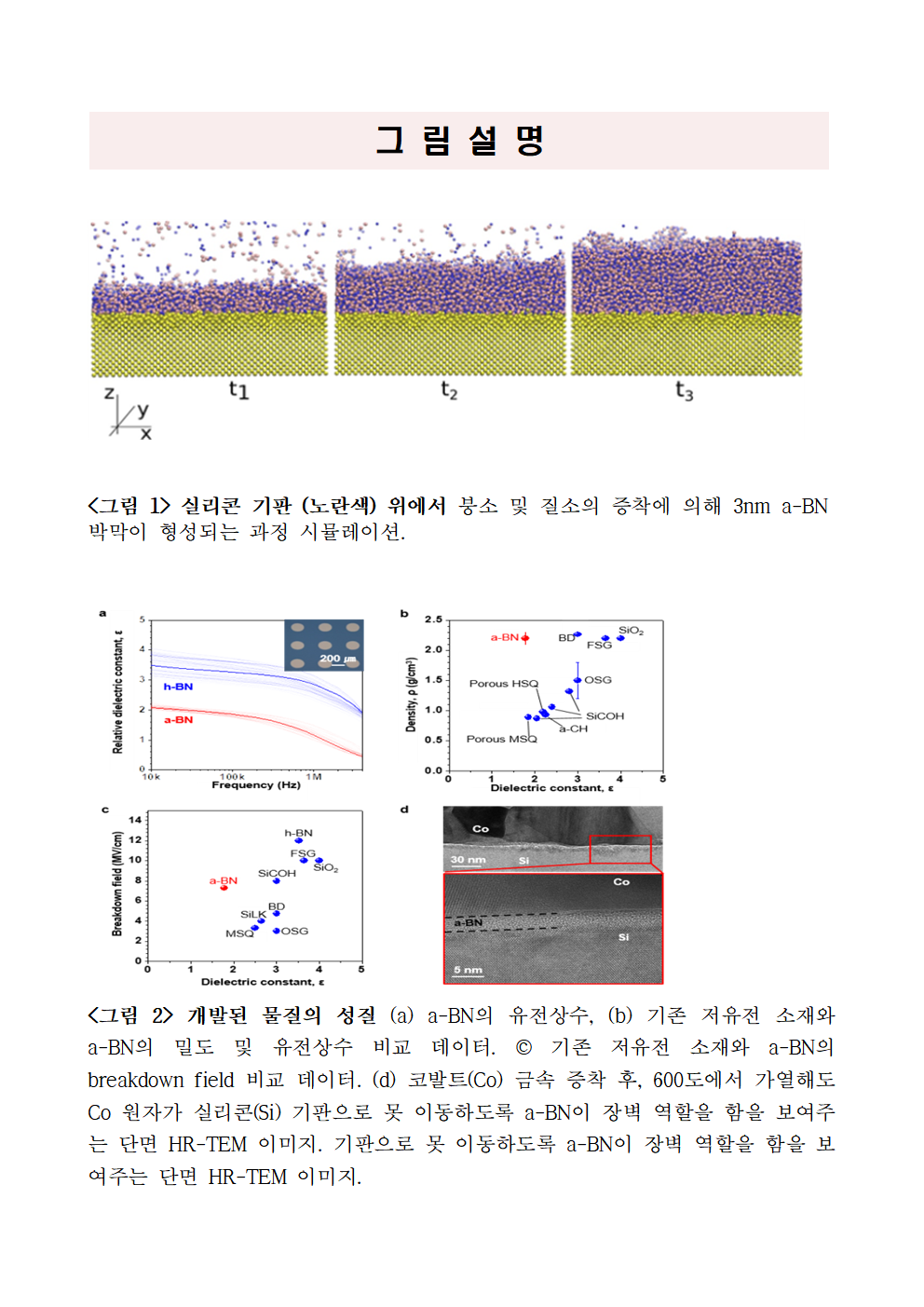

<그림 1> 실리콘 기판 (노란색) 위에서 붕소 및 질소의 증착에 의해 3nm a-BN 박막이 형성되는 과정 시뮬레이션.

<그림 2> 개발된 물질의 성질 (a) a-BN의 유전상수, (b) 기존 저유전 소재와 a-BN의 밀도 및 유전상수 비교 데이터. © 기존 저유전 소재와 a-BN의 breakdown field 비교 데이터. (d) 코발트(Co) 금속 증착 후, 600도에서 가열해도 Co 원자가 실리콘(Si) 기판으로 못 이동하도록 a-BN이 장벽 역할을 함을 보여주는 단면 HR-TEM 이미지. 기판으로 못 이동하도록 a-BN이 장벽 역할을 함을 보여주는 단면 HR-TEM 이미지.

연구자 이력사항 : 신현석 교수(교신저자)

1. 인적사항

○ 소 속: 울산과학기술원(UNIST)

2. 경력사항

○ 2003~2005년: POSTECH 박사후연구원

○ 2005~2006년: 영국 캐임브리지대학교 박사후연구원

○ 2007~2008년: POSTECH 연구교수

○ 2008년 7월~현재: UNIST 교수

○ 2014년 3월~2016년 2월: UNIST 기획처장

○ 2009년 3월~2018년 2월: UNIST 연구지원본부장

○ 2018년 1월~2019년 12월: UNIST 대외협력처장

3. 전문 분야 정보

○ 2차원 물질 합성 및 물리화학적 특성 분석

4. 연구지원정보

○ 기초연구실지원사업, 중견연구(전략)(과기정통부)

○ 글로벌프런티어지원사업(나노기반 소프트 일렉트로닉스연구, 과기정통부)

○ IBS 기초과학연구원

연구자 이력사항 : 신현진 박사(공동교신저자)

1. 인적사항

○ 소 속: 삼성전자 종합기술원 (SAIT)

2. 경력사항

○ 2018~현재: 삼성전자 종합기술원 Graphene Project Leader

○ 2016~현재: 삼성전자 종합기술원 Research Master

○ 2004~현재: 삼성전자 종합기술원 전문 연구원

3. 전문 분야 정보

○ 2차원 물질 합성 및 소자 개발

○ 초저유전 소재 개발 및 특성 분석

- 반도체 내부 전기 간섭 최소화하는 소재 개발로 집적도·성능 향상 가능 -

- 울산과학기술원-삼성전자 종합기술원 공동연구, 네이처 논문 게재 -

□ 반도체 칩 안의 소자를 “더 작게” 만들 수 있는 새로운 소재가 개발되었다. 이 소재를 이용하면 메모리와 같은 반도체 칩의 작동 속도를 “더 빠르게” 만들 수 있을 것으로 기대된다.

□ 울산과학기술원(UNIST) 자연과학부 신현석 교수팀이 삼성전자 종합기술원의 신현진 전문연구원팀, 기초과학연구원(IBS) 등과 국제공동연구를 통해 반도체 소자를 더 미세하게 만들 수 있는 ‘초저유전율* 절연체**’를 개발하는데 성공했다.

* 유전율 : 외부 전기장에 반응하는 민감도를 의미하며, 유전율이 낮으면 전기적 간섭이 줄어들어 반도체 소자 내 금속 배선(전류가 흐르는 길)의 간격을 줄일 수 있음

** 절연체 : 전류가 흐르지 않는 물질을 의미하며, 반도체 소자 내 금속 배선에서 전자가 다른 부분으로 이탈하는 것을 막기 위해 전자이동경로 사이에 절연체를 삽입함

◦ 반도체 소자의 크기를 줄임과 동시에 정보처리속도를 높일 수 있는 핵심적인 방법이 절연체의 유전율을 낮추는 것인데, 공동 연구팀이 기존 절연체 보다 30% 이상 낮은 유전율을 갖는 ‘비정질 질화붕소* (amorphous boron nitride) 소재’를 합성하는데 성공한 것이다.

* 원자 배치가 규칙적인 육방정계 질화붕소(일명 화이트그래핀)와 달리, 원자 배치가 불규칙한 질화붕소

◦ 과학기술정보통신부(장관 최기영)와 UNIST(총장 이용훈)는 이번 성과가 세계 최고 권위의 학술지 네이처(Nature, IF 43.070)에 6월 25일 0시(한국시간) 게재되었다고 밝혔다.

□ 현재와 같은 나노미터 단위의 반도체 공정에서는 소자가 작아질수록 내부 전기 간섭 현상이 심해져 오히려 정보처리 속도가 느려지게 된다. 이러한 이유로 전기 간섭을 최소화하는 낮은 유전율을 가진 신소재 개발이 반도체 한계 극복의 핵심이라고 알려져 있다.

<‘15년 국제반도체기술로드맵(ITRS: International Technology Roadmap for Semiconductors)>

‣트랜지스터의 세대가 거듭될수록 유전율이 낮은 절연체의 개발이 필수적이며, 초저유전율 소재 개발이 반도체 집적회로의 집적화의 한계점 중 하나임

◦ 현재 반도체 공정에서 사용되는 절연체는 다공성 유기규산염(p-SiCOH)으로 유전율이 2.5 수준이다. 이번에 공동연구팀이 합성한 비정질 질화붕소의 유전율은 1.78로 기술적 난제로 여겨진 유전율 2.5이하의 신소재를 발견한 것이며, 이를 통해 반도체 칩의 전력 소모를 줄이고 작동 속도도 높일 수 있을 것으로 기대된다.

◦ 연구팀은 이론적 계산 및 포항가속기연구소 4D 빔라인을 활용해 비정질 질화붕소의 유전율이 낮은 이유가 ‘원자 배열의 불규칙성’ 때문이라는 점도 밝혀냈다.

◦ 뿐만 아니라, 기존에는 유전율을 낮추기 위해 소재 안에 미세한 공기 구멍을 넣어 강도가 약해지는 문제가 있었으나, 비정질 질화붕소는 물질 자체의 유전율이 낮아 이러한 작업 없이도 높은 기계적 강도를 유지할 수 있게 되었다.

□ 제1저자인 홍석모 UNIST 박사과정 연구원은 “낮은 온도에서 육방정계 질화붕소(화이트 그래핀)가 기판에 증착되는지 연구하던 중 우연히 ‘비정질 질화붕소’의 유전율 특성을 발견했고, 반도체 절연체로써 적용 가능성을 확인했다”고 연구과정을 밝혔다.

ㅇ 교신저자인 신현석 UNIST 교수는 “이 물질이 상용화된다면 중국의 반도체 굴기와 일본의 수출 규제 등 반도체 산업에 닥친 위기를 이겨내는 데 큰 도움이 될 것”이라며 “‘반도체 초격차 전략’을 이어갈 수 있는 핵심 소재기술”이라고 강조했다.

◦ 또한 공동 교신저자인 신현진 삼성전자 종합기술원 전문연구원은 “이번 연구결과는 반도체 산업계에서 기술적 난제로 여겨지던 부분에 대해 학계와 산업계가 상호 협력을 통해 해결방안을 찾아낸 모범적인 사례”라고 말했다.

◦ 뿐만 아니라, 유럽연합의 그래핀 연구 프로젝트(Graphene Flagship)*파트너인 영국 케임브리지 대학교 매니쉬 초왈라 교수와 스페인 카탈루냐 나노과학기술연구소 스테판 로슈 교수가 참여하여 국제 공동연구로 진행되었으며,

* 그래핀을 포함한 2차원 물질에 대한 연구 프로젝트로 약 1조 3,592억원(10억유로)을 투자하는 유럽 연합의 최대 규모 연구 프로젝트

◦ 연구 수행은 과학기술정보통신부의 기초연구실, 중견연구(전략) 및 기초과학연구원(IBS), 삼성전자의 지원으로 이루어졌다.

연 구 결 과 개 요

□ 연구배경

반도체 소자1)의 고집적화가 가속화됨에 따라, 소자의 크기는 점점 작아졌다. 전통적으로 칩(Chip)의 성능(속도)은 트랜지스터2)의 스위칭 속도3)에 좌우됐으나, 소자의 크기가 작아지면서 빠른 스위칭 속도보다 배선 구조에서 발생하는 ‘신호전달 지연4)(RC delay: R은 금속 배선의 저항, C는 금속 배선 사이의 유전체 커패시턴스)’이 칩의 작동 성능을 좌우하게 됐다.

따라서 RC delay를 감소하기 위해 집적회로 백엔드 공정(BEOL ,back-end-of-line)5)의 금속 배선 사이에 증착되는 유전체(절연체)6)의 유전율7)을 줄이거나 금속배선의 전기저항 감소가 절대적으로 필요하다.

2015 ITRS 로드맵(미국 반도체 산업협회 발간하는 보고서)에 따르면, 트랜지스터의 세대가 거듭될수록 요구되는 유전물질(절연체)의 유전율은 감소하고 2028년에는 유전상수 2.0 이하의 유전체 개발이 필요하다. 하지만 현존 기술로는 불가능해, 초저유전 소재 개발이 IC칩(집적회로)의 집적화에서 한계점 중의 하나로 지목됐다.

□ 연구내용

연구팀은 플라즈마를 도입한 화학기상증착 방법을 이용해 실리콘(Si), 실리콘산화물(SiO₂), 구리(Cu) 등의 BEOL에 사용되는 기판에 3㎚ 두께의 매우 얇은 비정질 질화붕소(a-BN, amorphous BN) 8) 박막 증착에 성공했다.

a-BN을 고분해능 투과전자현미경(TEM)으로 관찰했을 때 기존에 보고된 a-BN보다 결정성이 낮았다. 광학적으로는 많이 연구된 육방정계 질화붕소(화이트 그래핀)와는 확연히 차이가 나는 광학적 물성을 보였다.

또한 a-BN을 이용해 간단한 전기소자(캐패시터)9)를 만들어 유전율을 측정해 보았는데, 기존에 보고된 여러 초저유전물질들과 비교했을 때 상당히 낮은 유전율(1.78, 100 KHz의 교류전류 주파수), 1.16 (1 MHz의 교류전류 주파수)을 나타냈다.

유전율뿐만 아니라 기존에 보고된 물질과 비교했을 때 기계적 물성도 우수하다. 일반적인 절연체로 사용되는 실리콘산화물과 유사한 고밀도로, 높은 강도 갖고 있으면 실리콘이나 구리 기판과의 접착력이 매우 높다.

금속 원자의 이동을 막는 금속 확산 방지막10)으로도 적용이 가능하다. 실리콘 기판 위에 형성된 a-BN 박막 위에 코발트(Co) 금속을 증착한 후 온도를 600℃로 올려 코발트 금속 원자가 a-BN을 뚫고 실리콘 기판으로 이동하는지를 보는 ‘베리어 평가’를 실시했는데, 코발트 금속의 이동을 완벽히 막아내는 매우 우수한 방지막의 특성을 보였다.

분자동역학(molecular dynamic simulation)을 이용한 이론적인 계산(NEXAFS)과 분석 등으로 근본적으로 물질의 극성이 무작위 방향으로 배열돼 있어 굉장히 낮은 유전율을 보이는 것으로 규명됐다.

□ 기대효과

배선금속과 초저유전물질이 들어가는 후공정(BEOL)은 메모리뿐만 아니라 비메모리까지 반도체 산업 전 영역에 걸쳐 사용되는 기술이다. 새로운 초유전물질의 개발은 감소하고 있는 초고밀도 집적회로(Very-large-scale integration; VLSI) 집적도의 상승세를 또 한 번 끌어올리고 소자의 소형화를 가속화 할 수 있는 원천기술이 될 것으로 기대한다.

용 어 설 명

1. 반도체 소자

반도체 소자는 실리콘과 같은 반도체(전기 흐름을 조절하는 물질), 금속(도체, 전기가 잘 통하는 물질), 절연체(부도체, 전기가 안 통하는 물질)등으로 구성돼 있다. 각종 전자제품에 들어가는 반도체 칩의 경우 단위 소자(회로) 여러 개가 집적돼 있다. 소자 집적도 높아지면 반도체의 정보 처리 속도 등이 빨라진다.

2. 트랜지스터(transistor)

전자 신호 및 전력을 증폭하거나 스위칭(회로를 연결했다 끊었다)하는 데 사용되는 반도체소자 중 하나.

3. 스위칭 속도

전자소자 안에 스위치 역할을 하는 트랜지스터의 구동 속도를 나타내는 단어로, 일반적으로 0과 1을 구현하는 논리소자의 연산속도를 대변하는 단어로 사용되고, BEOL의 유전체의 유전율과 배선 금속의 간격에 많은 영향을 받는다.

4. 신호전달지연(signal delay or RC delay)

금속 사이에 유전체(절연체)가 있는 상태에서 금속에 전류가 흐르게 되면 마주 보고 있는 두 금속 면에 전자 또는 전하가 축적되는 대전 현상이 발생한다. 대전된 두 금속 가까이 또 다른 전류가 흐르면 대전된 전하 때문에 발생하는 전기장의 간섭을 받고 전류가 흐르는 속도가 달라지는 현상이 생긴다. 초고밀도 집적회로에서 전극 금속 간의 거리가 가까워지게 되면 이러한 현상이 더욱 뚜렷하게 발생한다.

5. 유전체 (dielectric substance)

반도체에 들어가는 절연체를 이르는 다른 말. 물질은 전기전도도(전자가 얼마나 잘 이동하느냐)에 따라 도체, 반도체, 부도체(절연체)로 구분 된다.

6. 유전율 (permittivity)

전기가 통하지는 않는 부도체라도 외부의 전기장에 반응하는데, 그 반응의 민감도를 나타낸다. 자석의 N-S극처럼, 물질을 구성하는 분자는 전기쌍극자(electric dipole)가 있는데, 외부 전기장을 받으면 무질서하게 놓여있던 전기쌍극자가 정렬해 내부에 전기장이 발생한다. 이 전기장을 이용해 전하(전자)를 축적 할 수 있다. 단위부피당 유전율은 물질 고유의 특성이며, 유전상수로 나타낸다. 금속은 무한대의 유전상수를 갖으며, 공기의 유전상수가 가장 낮다. 때문에 기존 초 저유전체 연구에서는 절연체에 미세한 기공을 만들어 유전상수를 낮추는 방법이 주를 이뤘다. 이번 실험에서 합성된 비정질 질화붕소의 경우 전기쌍극자의 분포가 무질서해 유전상수가 낮다. 참고로 반도체의 소자 중 축전기에는 유전상수(High-k)가 높은 물질이 필요하다.

7. BEOL (back-end-of-line)

전체 반도체 공정 중에 후공정에서 만들어지는 구조로 전기 소자 위에 구리와 같은 전극 금속을 배열하여 원하는 전기소자를 올바르게 작동시키도록 전선을 이어주는 공정 또는 구조를 부르는 단어이다. 전극 금속끼리 맞닿게 되면 전기소자가 독립적으로 작동하지 않게 되는데 이를 방지하기 위해서 금속과 금속 사이에 초 저 유전물질을 삽입하여 전극 금속이 서로 닿지 않게 분리한다.

8. 비정질 질화붕소 (amorphous boron nitride)

원자 배열이 규칙적이지 않은 물질을 비정질이라 한다. (원자 배열이 규칙적인 물질은 결정이라 함). 규칙적인 원자 배열을 갖는 육방정계(6각형 벌집모양) 질화붕소의 경우 그래핀(벌집모양으로 탄소원자 배치된 2차원 물질)과 원자 배치 모양이 닮았지만 육안으로 하얗게 보여 ‘화이트 그래핀’으로 불린다.

9. 축전기 (Capacitor)

금속과 금속 사이에 유전체가 있는 구조로, 두 금속에 전압을 가하면 유전체의 유전율에 맞게 전하가 축적되는데 이런 현상을 이용하면 물질의 유전 상수를 구할 수 있다.

10. 금속 확산 방지막(metal barrier)

반도체 소자는 금속, 절연체, 반도체로 이루어져 있는데 금속의 경우 강한 전기장이나 열에너지를 받으면 원자들이 진동하게 되고, 이 진동을 원동력으로 금속 원자가 원래 위치에서 벗어나 절연체나 반도체 영역을 침범하고 화학적 결합을 이뤄 물질의 성질을 변화시킨다. 따라서 금속 확산을 막아줄 수 있는 물질을 금속과 다른 물질 사이에 삽입하는데, 이 물질을 금속 확산 방지막이라 한다.

그 림 설 명

<그림 1> 실리콘 기판 (노란색) 위에서 붕소 및 질소의 증착에 의해 3nm a-BN 박막이 형성되는 과정 시뮬레이션.

<그림 2> 개발된 물질의 성질 (a) a-BN의 유전상수, (b) 기존 저유전 소재와 a-BN의 밀도 및 유전상수 비교 데이터. © 기존 저유전 소재와 a-BN의 breakdown field 비교 데이터. (d) 코발트(Co) 금속 증착 후, 600도에서 가열해도 Co 원자가 실리콘(Si) 기판으로 못 이동하도록 a-BN이 장벽 역할을 함을 보여주는 단면 HR-TEM 이미지. 기판으로 못 이동하도록 a-BN이 장벽 역할을 함을 보여주는 단면 HR-TEM 이미지.

연구자 이력사항 : 신현석 교수(교신저자)

1. 인적사항

○ 소 속: 울산과학기술원(UNIST)

2. 경력사항

○ 2003~2005년: POSTECH 박사후연구원

○ 2005~2006년: 영국 캐임브리지대학교 박사후연구원

○ 2007~2008년: POSTECH 연구교수

○ 2008년 7월~현재: UNIST 교수

○ 2014년 3월~2016년 2월: UNIST 기획처장

○ 2009년 3월~2018년 2월: UNIST 연구지원본부장

○ 2018년 1월~2019년 12월: UNIST 대외협력처장

3. 전문 분야 정보

○ 2차원 물질 합성 및 물리화학적 특성 분석

4. 연구지원정보

○ 기초연구실지원사업, 중견연구(전략)(과기정통부)

○ 글로벌프런티어지원사업(나노기반 소프트 일렉트로닉스연구, 과기정통부)

○ IBS 기초과학연구원

연구자 이력사항 : 신현진 박사(공동교신저자)

1. 인적사항

○ 소 속: 삼성전자 종합기술원 (SAIT)

2. 경력사항

○ 2018~현재: 삼성전자 종합기술원 Graphene Project Leader

○ 2016~현재: 삼성전자 종합기술원 Research Master

○ 2004~현재: 삼성전자 종합기술원 전문 연구원

3. 전문 분야 정보

○ 2차원 물질 합성 및 소자 개발

○ 초저유전 소재 개발 및 특성 분석